# M4024

# LIQUID CRYSTAL DISPLAY MODULE

**USER'S MANUAL**

#### 1. GENERAL

#### 1.1 General

The M4024 is a low-power-consumption dot-matrix liquid crystal display (LCD) module with a high-contrast wide-view LCD panel and a CMOS LCD drive controller built in. The controller has a built-in character generator ROM/RAM, and display data RAM. All the display functions are controlled by instructions and the module can easily be interfaced with an MPU. This makes the module applicable to a wide range of purposes including terminal display units for microcomputers and display units for measuring gages.

#### 1.2 Features

- 40-character, four-line liquid crystal display of 5 x 7 dot matrix + cursor

- · Duty ratio: 1/16

- Character generator ROM for 192 character types (character font: 5 x 7 dot matrix)

- Character generator RAM for eight character types (program write)

(character font: 5 x 7 dot matrix)

- 80 x 8 bit x 2 display data RAM (160 characters maximum)

- · Interface with four-bit and eight-bit MPUs possible

- · Display data RAM and character generator RAM readable from MPU

- · Many instruction functions

Display Clear, Cursor Home, Display ON/OFF, Cursor ON/OFF, Display Character Blink, Cursor Shift, and Display Shift

- · Built-in oscillator circuit

- +5 V single power supply

- · Built-in automatic reset circuit at power-on

- · CMOS process

- Operating temperature range: 0°C to 50°C

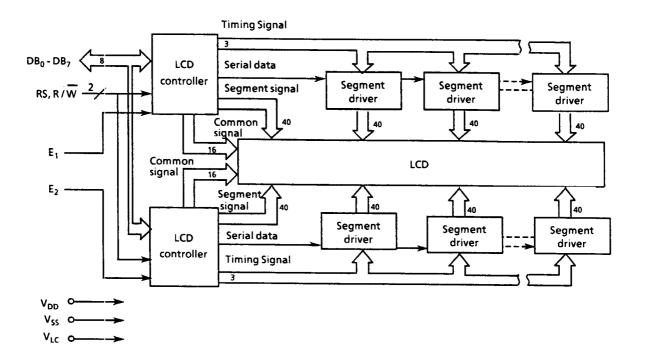

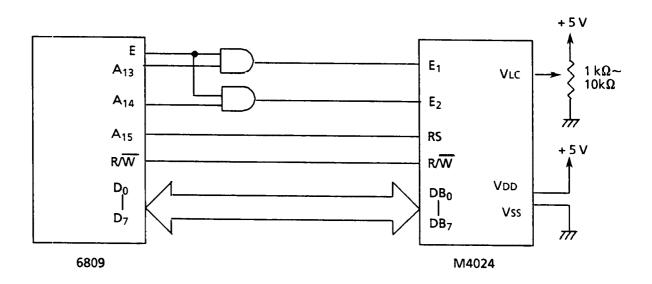

# 1.3 Block Diagram

Figure 1

## 1.4 Absolute Maximum Ratings

$V_{SS} = 0 V$

| Item Symbol            |                  | Standard                                | Unit | Remarks   |

|------------------------|------------------|-----------------------------------------|------|-----------|

| Power supply           | $V_{DD}$         | - 0.3 to + 6.5                          | V    |           |

| voltage                | V <sub>LC</sub>  | $V_{DD} - 6.5 \text{ to } V_{DD} + 0.3$ | V    |           |

| Input voltage          | V <sub>in</sub>  | - 0.3 to V <sub>DD</sub> + 0.3          | V    |           |

| Operating temperature  | T <sub>opr</sub> | 0 to +50                                | ℃    |           |

| Storage<br>temperature | T <sub>stg</sub> | - 20 to + 60                            | °C   | At 50% RH |

# 1.5 Electrical Characteristics

$V_{DD} = 5 V \pm 5\%$ ,  $V_{SS} = 0 V$ , Ta = 0°C to 50°C

| ltem                         | Item Symbol                 |                                  | Condition                    | Min. | Тур. | Max.            | Unit |  |

|------------------------------|-----------------------------|----------------------------------|------------------------------|------|------|-----------------|------|--|

| Input                        | Input High V <sub>IH1</sub> |                                  |                              | 2.2  | _    | V <sub>DD</sub> |      |  |

| voltage*                     | Low                         | V <sub>IL1</sub>                 |                              | 0    | _    | 0.6             |      |  |

| Output                       | High                        | V <sub>OH1</sub>                 | - I <sub>OH</sub> = 0.205 mA | 2.4  | _    | -               |      |  |

| voltage** Low V              |                             | V <sub>OL1</sub>                 | I <sub>OL</sub> = 1.2 mA     | _    | _    | 0.4             | V    |  |

| Power supply                 |                             | V <sub>DD</sub>                  |                              | 4.75 | 5.00 | 5.25            | V    |  |

| voltag                       | je                          | V <sub>DD</sub> -V <sub>LC</sub> |                              | 3.0  | _    | 6.0             | V    |  |

| Currer                       | nt                          | I <sub>DD</sub>                  |                              |      | 8.0  | 12.0            | mA   |  |

| consumption                  |                             | I <sub>LC</sub>                  | V <sub>LC</sub> = 0.25V      | _    | 3.0  | 4.5             | mA   |  |

| Clock oscillation freq. fosc |                             | fosc                             | Resistance oscillation       | 190  | 270  | 350             | kHz  |  |

<sup>\*</sup> Applied to  $DB_0$  to  $DB_7$ , E,  $R/\overline{W}$ , and RS

# Remark: Recommended operating voltage

The viewing angle and screen contrast of the LCD panel can be varied by changing the liquid crystal operating voltage ( $V_{\mbox{opr}}$ ), that is  $V_{\mbox{LC}}$ .

The optical characteristics is influenced by an ambient temperature. The recommended value of  $V_{\mbox{\scriptsize opr}}$  for an ambient temperatures are shown below.

| Temperature (℃)      | 0    | 10   | 25   | 40   | 50   |    |

|----------------------|------|------|------|------|------|----|

| V <sub>opr</sub> (V) | 5.00 | 4.90 | 4.75 | 4.60 | 4.50 | V, |

$$V_{opr} = V_{DD} - V_{LC}$$

<sup>\*\*</sup> Applied to DB<sub>0</sub> to DB<sub>7</sub>

# 1.6 Timing Characteristics

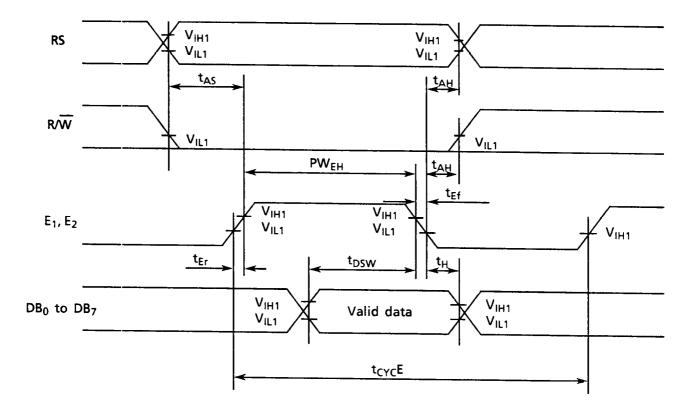

# 1.6.1 Write operation

| $V_{DD} = 5.0 \text{ V} \pm 5\%$ , $V_{SS} = 0 \text{ V}$ , $Ta = 0^{\circ}\text{C}$ to 50 | $V_{DD}$ | = . | 5.0 | ٧± | 5%, | $V_{SS}$ | = 0 | ٧, | Ta | = | 0°C | to | 50° |

|--------------------------------------------------------------------------------------------|----------|-----|-----|----|-----|----------|-----|----|----|---|-----|----|-----|

|--------------------------------------------------------------------------------------------|----------|-----|-----|----|-----|----------|-----|----|----|---|-----|----|-----|

| ltem                      |                                  | Symbol             | Min. | Max. | Unit |

|---------------------------|----------------------------------|--------------------|------|------|------|

| Enable cycle time         |                                  | t <sub>CYC</sub> E | 1000 | -    | ns   |

| Enable pulse width        | High level                       | PW <sub>EH</sub>   | 450  | _    | ns   |

| Enable rise and fall time | t <sub>Er</sub> ,t <sub>Ef</sub> | _                  | 25   | ns   |      |

| Setup time                | RS, $R/W \rightarrow E_1, E_2$   | t <sub>AS</sub>    | 140  | -    | ns   |

| Address hold time         |                                  | t <sub>AH</sub> 10 |      | -    | ns   |

| Data setup time           | t <sub>DSW</sub>                 | 195                | -    | ns   |      |

| Data hold time            | t <sub>H</sub>                   | 10                 | _    | ns   |      |

Figure 2 Data write from MPU to module

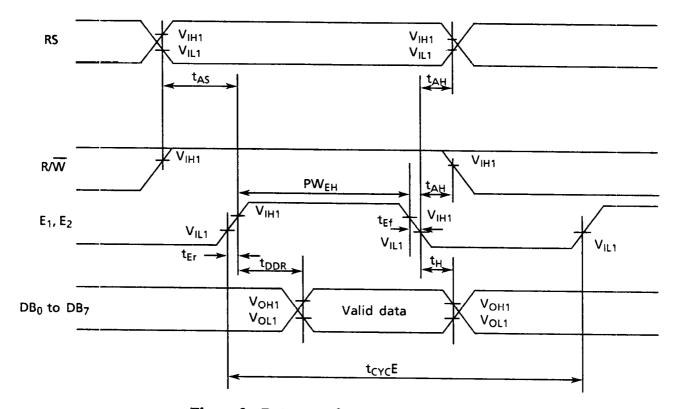

# 1.6.2 Read operation

| $V_{DD} = 5.0 V \pm 5\%,$ | $V_{SS} = 0 V_{A}$ | Ta = | 0°C to | 50° <b>C</b> |

|---------------------------|--------------------|------|--------|--------------|

|---------------------------|--------------------|------|--------|--------------|

| Item                      | 1                                 | Symbol                           | Min. | Max. | Unit |

|---------------------------|-----------------------------------|----------------------------------|------|------|------|

| Enable cycle time         |                                   | t <sub>CYC</sub> E               | 1000 | -    | ns   |

| Enable pulse width        | High level                        | PW <sub>EH</sub>                 | 450  | -    | ns   |

| Enable rise and fall time |                                   | t <sub>Er</sub> ,t <sub>Ef</sub> | _    | 25   | ns   |

| Setup time                | RS, $R/W \rightarrow E_1$ , $E_2$ | t <sub>AS</sub>                  | 140  | -    | ns   |

| Address hold time         | t <sub>AH</sub>                   | 10                               | -    | ns   |      |

| Data delay time           | t <sub>DDR</sub>                  | _                                | 320  | ns   |      |

| Data hold time            |                                   | t <sub>H</sub>                   | 20   | _    | ns   |

Figure 3 Data read from module to MPU

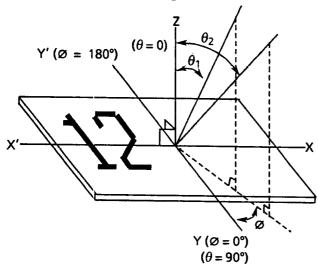

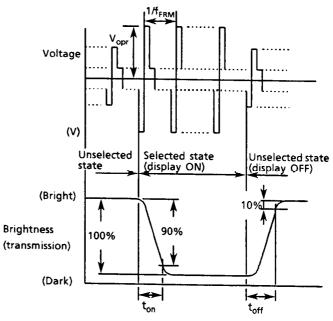

## 1.7 Optical Characteristics

# 1.7.1 Optical characteristics (TN LCD)

Viewing angle: 6 o'clock ( $\emptyset$  = 0°) Ta = 25°C, V<sub>opr</sub> = 4.75 V

| ltem                 | Symbol                | Conditions                                      | Min. | Тур.   | Max.   | Remarks            |

|----------------------|-----------------------|-------------------------------------------------|------|--------|--------|--------------------|

| Viewing angle        | $\theta_2 - \theta_1$ | $C \ge 2.0$ , $\emptyset = 0^{\circ}$           | 35   | -      | -      | See Notes 1 and 2. |

| Contrast             | С                     | $\theta$ = 25°, $\emptyset$ = 0°                | 5    | 8      | _      | See Note 3.        |

| Response time (rise) | ton                   | $\theta = 25^{\circ}$ , $\emptyset = 0^{\circ}$ |      | 60 ms  | 70 ms  | See Note 4.        |

| Response time (fall) | t <sub>off</sub>      | $\theta$ = 25°, $\varnothing$ = 0°              | _    | 150 ms | 170 ms | See Note 4.        |

Note 1: Definition of angles  $\varnothing$  and  $\theta$

Note 2: Definition of viewing angles  $\theta_1$  and  $\theta_2$

Contrast C

2.0  $\theta_1$ Viewing angle

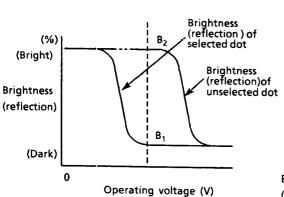

Note 3: Definition of contrast C

Brightness (reflection) of unselected dot (B2)

Brightness (reflection) of selected dot (B1)

Note 4: Definition of response time

$\begin{array}{lll} V_{opr}\colon & \text{Operating voltage} \\ f_{FRM}\colon & \text{Frame frequency} \\ t_{on}\colon & \text{Response time (rise)} \\ t_{off}\colon & \text{Response time (fall)} \end{array}$

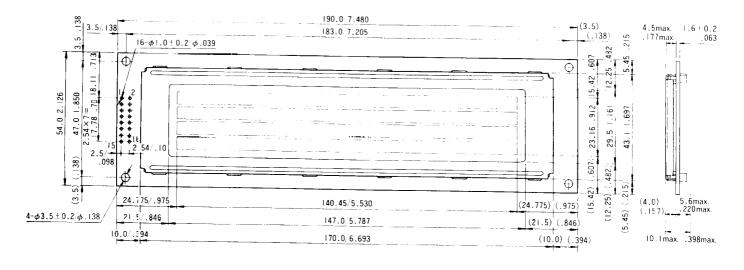

# 1.8 Dimensions

3.53/.139 2.78/.109 0.75/.030 0.50/.020 0.07/.003 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 200. 2 Unit: mm/inch

General tolerance: ± 0.5 mm

# I/O terminal symbol

| No. | Symbol          |

|-----|-----------------|

| 1   | DB <sub>7</sub> |

| 2   | DB <sub>6</sub> |

| 3   | DB <sub>5</sub> |

| 4   | DB <sub>4</sub> |

| 5   | DB <sub>3</sub> |

| 6   | DB <sub>2</sub> |

| 7   | DB <sub>1</sub> |

| 8   | DB <sub>0</sub> |

| 9   | E <sub>1</sub>  |

| 10  | R/W             |

| 11  | RS              |

| 12  | $V_{LC}$        |

| 13  | V <sub>SS</sub> |

| 14  | $V_{DD}$        |

| 15  | E <sub>2</sub>  |

| 16  | NC              |

Figure 4

# 2. OPERATING INSTRUCTIONS

# 2.1 Terminal Functions

Table 1 Terminal functions

| Signal name                        | No. of<br>terminals | 1/0   | Destination | Function                                                                        |

|------------------------------------|---------------------|-------|-------------|---------------------------------------------------------------------------------|

| DB <sub>0</sub> to DB <sub>3</sub> | 4                   | 1/0   | MPU         | Tristate bidirectional lower four data buses: Data                              |

|                                    |                     |       |             | is read from the module to the MPU or written to                                |

|                                    |                     |       | -           | the module from the MPU through the buses. If                                   |

|                                    |                     |       |             | the interface data is 4 bits, the signals are not used.                         |

| DB <sub>4</sub> to DB <sub>7</sub> | 4                   | 1/0   | MPU         | Tristate bidirectional upper four data buses: Data is                           |

|                                    |                     |       |             | read from the module to the MPU or written to the                               |

|                                    |                     |       |             | module from the MPU through the buses. DB <sub>7</sub> is also                  |

|                                    | <u> </u>            |       |             | used as a busy flag.                                                            |

| $E_1, E_2$                         | 2                   | Input | MPU         | Operation start signal. The signal activates data                               |

|                                    |                     |       |             | write or read: E <sub>1</sub> for the upper 2 lines, and E <sub>2</sub> for the |

|                                    |                     |       |             | lower 2 lines.                                                                  |

| R/W                                | 1                   | Input | MPU         | Read (R) and Write ( $\overline{\mathbf{W}}$ ) selection signals                |

|                                    |                     |       |             | 0: Write                                                                        |

|                                    | <u> </u>            |       |             | 1: Read                                                                         |

| RS                                 | 1                   | Input | MPU         | Register selection signals                                                      |

|                                    |                     |       |             | 0: Instruction register (Write)                                                 |

|                                    |                     |       |             | Busy flag and address counter (Read)                                            |

| ···                                |                     |       |             | 1: Data register (Write and Read)                                               |

| $V_{LC}$                           | 1                   | -     | Power       | Power supply terminal for driving liquid crystal                                |

|                                    |                     |       | supply      | display: The screen contrast can be varied by                                   |

|                                    | <u> </u>            |       |             | changing V <sub>LC</sub> .                                                      |

| $V_{DD}$                           | 1                   | _     | Power       | +5V                                                                             |

|                                    |                     |       | supply      |                                                                                 |

| $V_{SS}$                           | 1                   | _     | Power       | Ground terminal: 0 V                                                            |

|                                    | <u> </u>            |       | supply      |                                                                                 |

#### 2.2 Basic Operations

Since the M4024 has a controller for the upper two lines and a controller for the lower two lines, initialization and instructions (including Write Data to CG RAM or DD RAM and Read Data from CG RAM or DD RAM) are executed separately for the upper two and lower two lines. Upper and lower lines are selected by the E<sub>1</sub> and E<sub>2</sub> signals, so that the contents of the CG RAM or DD RAM of the controller for the upper two lines cannot be written or read with the controller for the lower two lines. The cursor does not move continuously from the second line to the third line.

## 2.2.1 Registers

The controller has two kinds of eight-bit registers: the instruction register (IR) and the data register (DR). They are selected by the register select (RS) signal as shown in Table 2.

The IR stores instruction codes such as Display Clear and Cursor Shift, and the address information of display data RAM (DD RAM) and character generator RAM (CG RAM). They can be written from the MPU, but cannot be read to the MPU.

The DR temporarily stores data to be written into DD RAM or CG RAM, or read from DD RAM or CG RAM. When data is written into DD RAM or CG RAM from the MPU, the data in the DR is automatically written into DD RAM or CG RAM by internal operation. However, when data is read from DD RAM or CG RAM, the necessary data address is written into the IR. The specified data is read out to the DR and then the MPU reads it from the DR. After the read operation, the next address is set and DD RAM or CG RAM data at the address is read into the DR for the next read operation.

Table 2 Register selection

| RS | RW | 0                                      | peration                                               |

|----|----|----------------------------------------|--------------------------------------------------------|

| 0  | 0  | IR selection, IR write.                | Internal operation: Display clear                      |

| 0  | 11 | Busy flag (DB <sub>7</sub> ) and addre | ess counter (DB <sub>0</sub> to DB <sub>6</sub> ) read |

| 1  | 0  | DR selection, DR write.                | Internal operation : DR to DD RAM or CG RAM            |

| 1  | 1  | DR selection, DR read.                 | Internal operation : DD RAM or CG RAM to DR            |

# 2.2.2 Busy flag (BF)

The flag indicates whether the module is ready to accept the next instruction. As shown in Table 2, the signal is output to DB7 if RS = 0 and  $R/\overline{W}$  = 1. If the value is 1, the module is working internally and the instruction cannot be accepted. If the value is 0, the next instruction can be written. Therefore, the flag status needs to be checked before executing an instruction. If an instruction is executed without checking the flag status, wait for more than the execution time shown by 2.4 Instruction Outline.

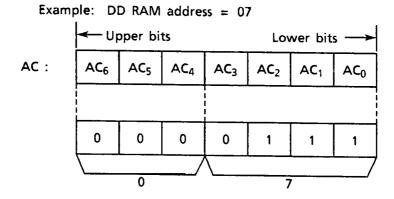

## 2.2.3 Address counter (AC)

The counter specifies an address when data is written into DD RAM or CG RAM and the data stored in DD RAM or CG RAM is read out. If an Address Set instruction (for DD RAM or CG RAM) is written in the IR, the address information is transferred from the IR to the AC. When display data is written into or read from DD RAM or CG RAM, the AC is automatically incremented or decremented by one according to the Entry Mode Set. The contents of the AC are output to DB0 to DB6 as shown in Table 2 if RS = 0 and R/W=1.

## 2.2.4 Display data RAM (DD RAM)

DD RAM has a capacity of up to  $80 \times 8$  bits and stores display data of 80 eight-bit character codes. M4024 has two controllers and its capacity is 160 characters. Some storage areas of DD RAM which are not used for display can be used as general data RAM.

A DD RAM address to be set in the AC is expressed in hexadecimal form as follows.

DD RAM addresses  $00_{\rm H}$  to  $27_{\rm H}$  are set in the lines 1 and 3, and  $40_{\rm H}$  to  $67_{\rm H}$  in the lines 2 and 4.

Note: The addresses in the digit 40 of line 1 and the digit 1 of line 2 are not consecutive. Also, the addresses in the digit 40 of line 3 and the digit 1 of line 4 are not consecutive.

|        | 1  | 2  | 3  | 4  | 5  | 6  | 7  |   | 34  | 35 | 36 | 37 | 38      | 39 | 40 | Display digit     |

|--------|----|----|----|----|----|----|----|---|-----|----|----|----|---------|----|----|-------------------|

| Line 1 | 00 | 01 | 02 | 03 | 04 | 05 | 06 |   | 21  | 22 | 23 | 24 | 25      | 26 | 27 | DD RAM<br>address |

| Line 2 | 40 | 41 | 42 | 43 | 44 | 45 | 46 |   | 61  | 62 | 63 | 64 | 65      | 66 | 67 | addi ess          |

|        | ι  |    |    | г  | Ţ  | T  |    | 1 | т - |    |    |    | · · · · |    |    | `<br>}            |

| Line 3 | 00 | 01 | 02 | 03 | 04 | 05 | 06 |   | 21  | 22 | 23 | 24 | 25      | 26 | 27 |                   |

| Line 4 | 40 | 41 | 42 | 43 | 44 | 45 | 46 |   | 61  | 62 | 63 | 64 | 65      | 66 | 67 |                   |

If the display is shifted to right with  $E_1$  activated, DD RAM address moves as follows.

|         | 1   | 2  | 3  | 4  | 5   | 6   | 7   |          | 34 | 35 | 36 | 37 | 38 | 39 | 40 | Display digit |

|---------|-----|----|----|----|-----|-----|-----|----------|----|----|----|----|----|----|----|---------------|

| Line 1  | 27  | 00 | 01 | 02 | 03  | 04  | 05  |          | 20 | 21 | 22 | 23 | 24 | 25 | 26 | DD RAM        |

| Line 2  | 67  | 40 | 41 | 42 | 43  | 44  | 45  |          | 60 | 61 | 62 | 63 | 64 | 65 | 66 | address       |

| Line 3  | 00  | 01 | 02 | 00 | 0.4 | 0.5 | 0.5 | <u> </u> |    | Γ  | T  |    |    | 1  |    | 1             |

| rille 2 | -00 | v. | 02 | 03 | 04  | 05  | 06  |          | 21 | 22 | 23 | 24 | 25 | 26 | 27 |               |

| Line 4  | 40  | 41 | 42 | 43 | 44  | 45  | 46  |          | 61 | 62 | 63 | 64 | 65 | 66 | 67 |               |

If the display is shifted to right with  $E_2$  activated, DD RAM address moves as follows.

| ,      | 1  | 2  | 3          | 4  | 5  | 6  | 7  |   | 34 | 35 | 36 | 37 | 38 | 39 | 40 | Display digit |

|--------|----|----|------------|----|----|----|----|---|----|----|----|----|----|----|----|---------------|

| Line 1 | 00 | 01 | 02         | 03 | 04 | 05 | 06 |   | 21 | 22 | 23 | 24 | 25 | 26 | 27 | DD RAM        |

| Line 2 | 40 | 41 | 42         | 43 | 44 | 45 | 46 |   | 61 | 62 | 63 | 64 | 65 | 66 | 67 | address       |

|        | г  |    | 9098000000 | -  |    |    |    | , |    |    |    |    |    |    |    |               |

| Line 3 | 27 | 00 | 01         | 02 | 03 | 04 | 05 |   | 20 | 21 | 22 | 23 | 24 | 25 | 26 |               |

| Line 4 | 67 | 40 | 41         | 42 | 43 | 44 | 45 |   | 60 | 61 | 62 | 63 | 64 | 65 | 66 |               |

All four lines cannot be shifted at the same time. Instructions must be written using  $E_1$  and  $E_2$  to distinguish the upper two lines from the lower two lines.

# 2.2.5 Character generator ROM (CG ROM)

Character generator ROM generates 192 types of 5 x 7 dot-matrix character patterns from eight-bit character codes.

Table 3 shows the correspondence between the CG ROM character codes and character patterns.

# 2.2.6 Character generator RAM (CG RAM)

CG RAM is used to create character patterns freely by programming. Eight types of character patterns can be written.

Table 4 shows the character patterns created from CG RAM addresses and data. To display a created character pattern, the character code in the left column of the table is written into DD RAM corresponding to the display position (digit). The areas not used for display are available as general data RAM.

Table 3 Correspondence between character codes and character patterns

|                                    | ie o             |      | E                                       |             |       |             |            | des an | <b>C C I C I C C I C C C C C C C C C C</b> | uctor .     | parter       |              |       |

|------------------------------------|------------------|------|-----------------------------------------|-------------|-------|-------------|------------|--------|--------------------------------------------|-------------|--------------|--------------|-------|

| Upper<br>4 bits<br>Lower<br>4 bits | 0000             | 0010 | 0011                                    | 0100        | 0101  | 0110        | 0111       | 1010   | 1011                                       | 1100        | 1101         | 1110         | 1111  |

| ××××0000                           | CG<br>RAM<br>(1) |      |                                         | :::         |       | ٠.          |            |        | ••••                                       |             | :::.         |              | :::   |

| ××××0001                           | (2)              | •    | :                                       |             |       |             | •:::       | :::    |                                            | <b>::</b> . | ··           |              |       |

| ××××0010                           | (3)              | ::   |                                         |             |       | :           | ···.       | :"     | .:                                         | :::         |              | ::::         |       |

| ××××0011                           | (4)              |      | • • • • • • • • • • • • • • • • • • • • |             | ::    | <b>:</b> .  | :::.       |        | :::                                        | :           |              | <b>:::</b> . | ::•:: |

| ××××0100                           | (5)              |      | <b>::</b>                               |             | ••••  |             | <b>:</b>   | ٠.     |                                            | <b>!·</b> · | •            |              | :::   |

| ××××0101                           | (6)              | ::.· | ::                                      |             |       | ::::        | <b>i</b> i | ::     |                                            |             |              |              |       |

| ××××0110                           | (7)              |      | :::::                                   |             | ii    |             | i.,:       |        |                                            | •••         |              |              | ::    |

| ××××0111                           | (8)              | ::   | ::                                      |             |       | :           | ii         |        |                                            |             |              |              |       |

| ××××1000                           | (1)              | ::   |                                         |             | ::::: |             | :::        | .:     | :                                          |             |              |              |       |

| ××××1001                           | <u>{2</u> }      |      | :                                       |             | 1,1   | i           | ii         | iriri  | ••••                                       | .:          | •            | :            | ••    |

| ××××1010                           | (3)              | :4:: | ::                                      |             | ::::  |             |            |        |                                            | •           | <b>i.</b> .· |              |       |

| ××××1011                           | (4)              | •••• | ::                                      | <b>!</b> :: |       | <b>!</b> :: | ·          |        |                                            |             |              | :::          | :-:   |

| ××××1100                           | (5)              | ::   | ::                                      | <b></b>     |       |             |            | ::::   | <b></b> :                                  | :           |              | :::.         |       |

| ××××1101                           | (6)              | •••• | ••••                                    |             |       | :::         | :          |        |                                            | •••:        |              |              |       |

| ××××1110                           | (7)              | ::   |                                         | • • •       | ···   |             | :          |        |                                            | ::::        | •.••         | •••          |       |

| ××××1111                           | (8)              |      | •::                                     |             |       | ::::        | •:••       | :::    | ·•                                         |             | :::          |              |       |

Character code Character pattern (CG RAM data) CG RAM address (DD RAM data) 5 4 \_ Upper bit 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0 **←**Upper bit Lower bit Lower bit Upper bit Lower bit 0 0 Example of 0 0 0 character 0000 \* 000 pattern (R) n 0 10 0 0 0 0 0 0 0 ← Cursor position 0 1 0 1 0 Example of 0000 \* 001 0 0 11 0 0 character pattern (¥) 0 ;0 0 **11** 0 0 0000 \* 111

Table 4 Relationships between CG RAM addresses and character codes (DD RAM) and character patterns (CG RAM data)

Notes: In CG RAM data, 1 corresponds to Selection and 0 to Non-selection on the display.

- · Character code bits 0 to 2 and CG RAM address bits 3 to 5 correspond with each other (three bits, eight types).

- · CG RAM address bits 0 to 2 specify a line position for a character pattern. Line 8 of a character pattern is the cursor position where the logical sum of the cursor and CG RAM data is displayed. Set the data of line 8 to 0 to display the cursor. If the data is changed to 1, one bit lights, regardless of the cursor.

- The character pattern column positions correspond to CG RAM data bits 0 to 4 and bit 4 comes to the left end. CG RAM data bits 5 to 7 are not displayed but can be used as general data RAM.

- When reading a character pattern from CG RAM, set to 0 all of character code bits 4 to 7. Bits 0 to 2 determine which pattern will be read out. Since bit 3 is not valid, 00H and 08H select the same character.

#### 2.3 Instruction Outline

Table 5 List of instructions

| Instruction                                |    |     |                 |                 | Co              | de              |                 |                 |                 |                 |                                                                                                              | Execu-        |

|--------------------------------------------|----|-----|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|--------------------------------------------------------------------------------------------------------------|---------------|

| instruction                                | RS | R/W | DB <sub>7</sub> | DB <sub>6</sub> | DB <sub>5</sub> | DB <sub>4</sub> | DB <sub>3</sub> | DB <sub>2</sub> | DB <sub>1</sub> | DB <sub>0</sub> | Function                                                                                                     | tion<br>time# |

| (1) Display clear                          | 0  | 0   | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 1               | Clears all display and returns cursor to home position (address 0)                                           | 1.64 ms       |

| (2) Cursor Home                            | 0  | 0   | 0               | 0               | 0               | 0               | 0               | 0               | 1               | *               | Returns cursor to home position. Shifted display returns to home position and DD RAM contents do not change. | 1.64 ms       |

| (3) Entry Mode Set                         | 0  | 0   | 0               | 0               | 0               | 0               | 0               | 1               | I/D             | s               | Sets direction of cursor movement and whether display will be shifted when data is written or read           | 40 µS         |

| (4) Display ON / OFF control               | o  | 0   | 0               | 0               | 0               | 0               | 1               | D               | С               | В               | Turns ON/OFF total display (D) and cursor (C), and makes cursor position column start blinking (B)           | 40 µ <b>s</b> |

| (5) Cursor/Display Shift                   | 0  | 0   | 0               | 0               | 0               | 1               | s/c             | R/L             |                 | *               | Moves cursor and shifts display without changing DD RAM contents                                             | 40 µS         |

| (6) Function Set                           | 0  | 0   | 0               | 0               | 1               | DŁ              | N               | F               |                 | *               | Sets interface data length (DL), the number of display lines (N), and character fonts (F)                    | 40 µS         |

| (7) CG RAM Address                         | 9  | ç   | 8               | 1               |                 |                 | Д               | cG              |                 | <b>-</b>        | Sets CG RAM address to start transmitting                                                                    | 48 jiš        |

| (8) DD RAM Address<br>Set                  | 0  | 0   | 1               |                 |                 |                 | A <sub>DD</sub> |                 |                 |                 | Sets DD RAM address to start transmitting or receiving DD RAM data                                           | 40 µs         |

| (9) BF/Address Read                        | 0  | 1   | BF              |                 |                 |                 | AC              |                 |                 |                 | Reads BF indicating module in internal operation and AC contents (used for both CG RAM and DD RAM)           | 0 µs          |

| (10) Data Write to CG<br>RAM or DD RAM     | 1  | 0   |                 |                 | _               | Vrite           | Dat             | a               |                 |                 | Writes data into DD RAM or CG RAM                                                                            | 40 µS         |

| (11) Data Read from<br>CG RAM or DD<br>RAM | 1  | 1   |                 |                 | ı               | Read            | Data            | 3               |                 |                 | Reads data from DD RAM or CG RAM                                                                             | 40 µS         |

\* : Invalid bit A<sub>CG</sub> : CG RAM address

I/D = 1 : Increment

I/D = 0 : Decrement

B = 1 : Blink ON

N = 1 : 2 lines

A<sub>DD</sub>: DD RAM address

AC: Address counter

\_

B = 0 : Blink OFF

N = 0 : 1 line

S = 1 : Display shift

S/C = 1 : Display shift

S = 0: No display shift S/C = 0:

S/C = 0 : Cursor movement

F = 1 :  $5 \times 10$  dot matrix F = 0 :  $5 \times 7$  dot matrix

D = 1 : Display ON D = 0 : Display OFF

R/L = 1: Right shift

BF = 1 : Internal operation

R/L = 0: Left shift

in progress

BF = 0 : Instruction can be

C = 1 : Cursor ON

DL = 1 : 8 bits

accepted

C = 0 : Cursor OFF

DL = 0 : 4 bits

<sup>#</sup> An execution time indicates maximum value when  $f_{osc}$  is 250 kHz. It changes at the inverse proportion of  $f_{osc}$

#### 2.4 Instruction Details

## (1) Display Clear

|      | RS | R/W | DB <sub>7</sub> |   | ······································ |   |   | - |   | $DB_0$ |  |

|------|----|-----|-----------------|---|----------------------------------------|---|---|---|---|--------|--|

| Code | 0  | 0   | 0               | 0 | 0                                      | 0 | 0 | 0 | 0 | 1      |  |

Bisplay Clear Clears all display and returns curson to home position (address 0).

Space code 20 (hexadecimal) is written into all the addresses of DD RAM, and DD RAM address 0 is set to the AC. If shifted, the display returns to the original position. After execution of the Display Clear instruction, the entry mode is incremented.

Note: When executing the Display Clear instruction, follow the restrictions listed in Table 6.

#### (2) Cursor Home

|      | RS | R/W | DB <sub>7</sub> |   |   |   |   |   |   | $DB_0$ |                    |

|------|----|-----|-----------------|---|---|---|---|---|---|--------|--------------------|

| Code | 0  | 0   | 0               | 0 | 0 | 0 | 0 | 0 | 1 | *      | * : Don't care bit |

Cursor Home returns cursor to home position (address 0).

DD RAM address 0 is set to the AC. The cursor returns to the home position. If shifted, the display returns to the original position. The DD RAM contents do not change. If the cursor or blinking is ON, it returns to the left side.

Note: When executing the Cursor Home instruction, follow the restrictions listed in Table 6.

Table 6 Restrictions on execution of Display Clear and Cursor Home instructions

| Conditions of use                                                                                                                               | Restrictions                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| When executing the Display Clear or Cursor<br>Home instruction when the display is<br>shifted (after execution of Display Shift<br>instruction) | The Cursor Home instruction should be executed again immediately after the Display Clear or Cursor Home instruction is executed. Do not leave an interval of a multiple of $400/f_{osc}^*$ second after the first execution. Example: 1.5 ms, 3.0 ms, 4.5 ms for $f_{osc} = 150$ kHz * $f_{osc}$ : Oscillation frequency                   |

| When 23 <sub>H</sub> , 27 <sub>H</sub> , 63 <sub>H</sub> , or 67 <sub>H</sub> is used as a DD RAM address to execute Cursor Home instruction    | Before executing the Cursor Home instruction, the data of the four DD RAM addresses given at the left should be read and saved. After execution, write the data again in DD RAM. (This restriction is necessary to prevent the contents of the DD RAM addresses from being destroyed after the Cursor Home instruction has been executed.) |

#### (3) Entry Mode Set

|      | RS | R/W | DB <sub>7</sub> |   |   |   |   |   |     | $DB_0$ |  |

|------|----|-----|-----------------|---|---|---|---|---|-----|--------|--|

| Code | 0  | 0   | 0               | 0 | 0 | 0 | 0 | 1 | I/D | S      |  |

Entry Mode Set sets the direction of cursor movement and whether display will be shifted.

I/D: The DD RAM address is incremented or decremented by one when a character code is written into or read from DD RAM. This is also true for writing into or reading from CG RAM.

When I/D = 1, the address is incremented by one and the cursor or blink moves to the right.

When I/D = 0, the address is decremented by one and the cursor or blink moves to the left.

S: If S = 1, the entire display is shifted either to the right or left for writing into DD RAM. The cursor position does not change, only the display moves. There is no display shift for reading from DD RAM.

When S = 1 and I/D = 1, the display shifts to the left.

When S = 1 and I/D = 0, the display shifts to the right.

If S = 0, the display does not shift.

#### (4) Display ON/OFF Control

|      | RS | R/W | DB <sub>7</sub> |   |   |   |   |   |   | $DB_0$ |

|------|----|-----|-----------------|---|---|---|---|---|---|--------|

| Code | 0  | 0   | 0               | 0 | 0 | 0 | 1 | D | C | В      |

Display ON/OFF Control turns the total display and the cursor ON and OFF, and makes the cursor position start blinking. Cursor ON/OFF and blinking is done at the column indicated by the specified DD RAM address by the AC.

D: When D = 1, the display is turned ON.

When D = 0, the display is turned OFF.

If D = 0 is used, display data remains in DD RAM. Change 0 to 1 to display data.

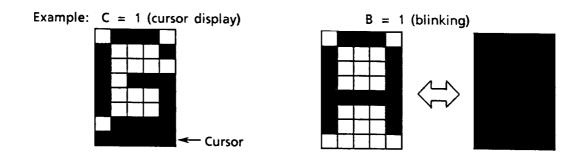

- C: When C = 1, the cursor is displayed.

When C = 0, the cursor is not displayed.

The cursor is displayed in the dot line below the character fonts.

- B: When B = 1, the character at the cursor position starts blinking. When B = 0, it does not blink. For blinking, all-black dots and the character are switched about every 0.4 seconds when  $f_{\rm OSC}$  is 250 kHz. The cursor and blinking can be set at the same time.

## (5) Cursor/Display Shift

|      | RS | R/W | DB <sub>7</sub> |   |   |   | ·   | <u>-</u> - |   | DB <sub>0</sub> |                    |

|------|----|-----|-----------------|---|---|---|-----|------------|---|-----------------|--------------------|

| Code | 0  | 0   | 0               | 0 | 0 | 1 | S/C | R/L        | * | *               | * : Don't care bit |

Cursor/Display Shift moves the cursor and shifts the display without changing the DD RAM contents.

The cursor position and the AC contents match. This instruction is available for display correction and retrieval because the cursor position or display can be shifted without writing or reading display data. The cursor is shifted from digit 40 of line 1 to digit 1 of line 2. Displays of lines 1 and 2 are shifted at the same time. Also the cursor is shifted from digit 40 of line 3 to digit 1 of line 4. Displays of lines 3 and 4 are shifted at the same time. Therefore, the display pattern of line 2 or 4 is not shifted to line 1 or 3(see 2.2.4 Display Data RAM).

| S/C | R/L | Operation                                                           |

|-----|-----|---------------------------------------------------------------------|

| 0   | 0   | The cursor position is shifted to the left (the AC decrements one)  |

| 0   | 1   | The cursor position is shifted to the right (the AC increments one) |

| 11  | 0   | The entire display is shifted to the left with the cursor           |

| 1   | 1   | The entire display is shifted to the right with the cursor          |

Note: If only display shift is done, the AC contents do not change.

#### (6) Function Set

|      | RS | R/W | DB <sub>7</sub> |   |   | ·  |   |   |   | $DB_0$ |                    |

|------|----|-----|-----------------|---|---|----|---|---|---|--------|--------------------|

| Code | 0  | 0   | 0               | 0 | 1 | DL | N | F | * | *      | * : Don't care bit |

Function Set sets the interface data length, the number of display lines, and the character font.

DL: Interface data length

When DL = 1, the data length is set at eight bits (DB7 to DB0).

When DL = 0, the data length is set at four bits (DB7 to DB4).

The upper four bits are transferred first, then the lower four bits follow.

N: Number of display lines

When N = 1, the display line is set to two lines.

When N = 0, the display line is set to one line.

Since M4024 is regarded as two two-line displays, so set N to 1.

F: Character font

When F = 1, the character font is set to  $5 \times 10$  dot matrix.

When F = 0, the character font is set to  $5 \times 7$  dot matrix.

If N is set to 1, F becomes "Don't care bit". For M4024, set F to 0 or 1.

The Function Set instruction must be executed prior to all other instructions except for Busy Flag/Address Read. If another instruction is executed first, no function instruction except changing the interface data length can be executed.

#### Remarks: Initialization

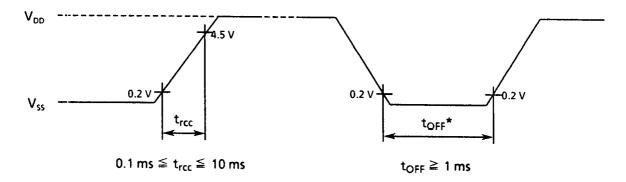

## 1. Automatic initialization

The system is automatically initialized at power-on if the following power supply conditions are satisfied.

\*t<sub>OFF</sub>: Time when power supply is OFF if cut instantaneously or turned ON and OFF repeatedly

The following instructions are executed for initialization.

· Display Clear

• Function Set

DL = 1: Interface data length: Eight bits

N=0: One line display

F=0: Character font:  $5 \times 7$  dot matrix

• Display ON/OFF Control

D = 0: Display OFF

C = 0: Cursor OFF

B = 0: Blink OFF

• Entry Mode Set

I/O = 1: Increment

S = 0: No display shift

Since the condition is not suitable for the M4024, further Function Set instruction is necessary.

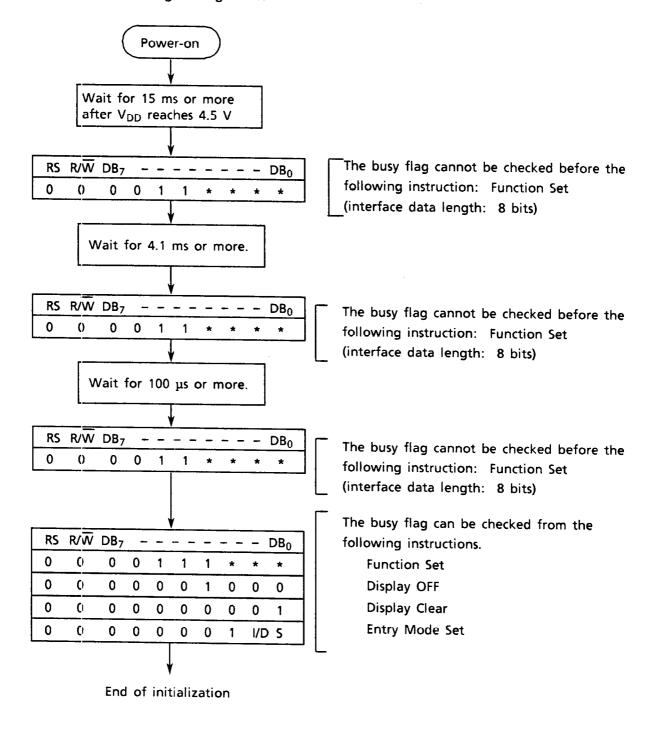

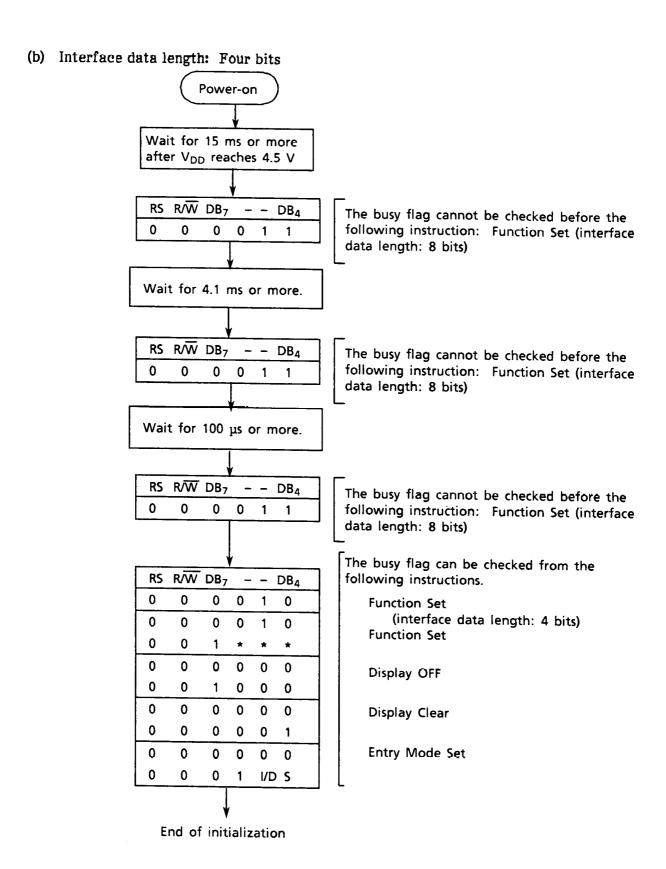

## 2. Initialization by instructions

If automatic initialization is not executed because the above power supply conditions are not satisfied, use the following instructions. Since it is unknown whether the interface data length is set to eight bits or four bits at power on, execute Function Set twice to set the interface data length to eight bits. And then for setting the required interface data length execute further Function Set instruction.

## (a) Interface data length: Eight bits

<sup>\*</sup>Note: Initialization has to be executed twice, for  $E_1$  and for  $E_2$ .

<sup>\*</sup>Note: Initialization has to be executed twice, for  $E_1$  and for  $E_2$ .

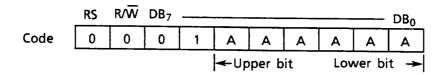

#### (7) CG RAM Address Set

CG RAM addresses expressed as binary AAAAAA are set to the AC. Then data in CG RAM is written from or read to the MPU.

#### (8) DD RAM Address Set

DD RAM addresses expressed as binary AAAAAAA are set to the AC. Then data in DD RAM is written from or read to the MPU. The addresses used for display in lines 1 and 3 (AAAAAAA) are 00H to 27H and those for lines 2 and 4 (AAAAAAA) are 40H to 67H.

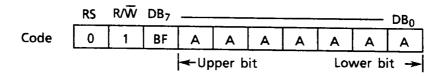

# (9) Busy Flag/Address Read

The BF signal is read out, indicating that the module is working internally because of the previous instruction.

When BF = 1, the module is working internally and the next instruction cannot be accepted until the BF value becomes 0.

When BF = 0, the next instruction can be accepted.

Therefore, make sure that BF = 0 before writing the next instruction. The AC values of binary AAAAAA are read out at the same time as reading the busy flag. The AC addresses are used for both CG RAM and DD RAM but the address set before execution of the instruction determines which address is to be used.

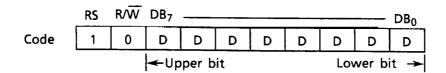

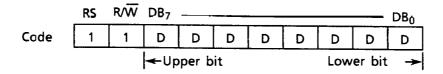

#### (10) Data Write to CG RAM or DD RAM

Binary eight-bit data DDDDDDDD is written into CG RAM or DD RAM. The CG RAM Address Set instruction of (7) or the DD RAM Address Set instruction of (8) before this instruction selects either RAM. After the write operation, the address and display shift are determined by the entry mode setting.

#### (11) Data Read from CG RAM or DD RAM

Binary eight-bit data DDDDDDDD is read from CG RAM or DD RAM. The CG RAM Address Set instruction of (7) or the DD RAM Address Set instruction of (8) before this instruction selects either RAM. In addition, either instruction (7) or (8) must be executed immediately before this instruction. If no address set instruction is executed before a read instruction, the first data read becomes invalid. If read instructions are executed consecutively, data is normally read from the second time. However, if the cursor is shifted by the Cursor Shift instruction when reading DD RAM, there is no need to execute an address set instruction because the Cursor Shift instruction does this.

After the read operation, the address is automatically incremented or decremented by one according to the entry mode, but the display is not shifted.

Note: The AC is automatically incremented or decremented by one according to the entry mode after a write instruction is executed to write data in CG RAM or DD RAM. However, the data of the RAM selected by the AC are not read out even if a read instruction is executed immediately afterwards.

Correct data is read out under the following conditions.

- · An address set instruction is executed immediately before readout.

- For DD RAM, the Cursor Shift instruction is executed immediately before readout.

- The second, or later, instruction is executed in consecutive execution of read instructions.

# 2.5 Examples of Instruction Use

# 2.5.1 Interface data length: Eight bits

| No. | Instruction                                                                                                                                                       | Display | Operation                                                                                                                                                    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Power-on  E RS R/W DB <sub>7</sub> — DB <sub>0</sub>                                                                                                              |         | The built-in reset circuit initializes the module.                                                                                                           |

| 2   | Function Set  E RS R/W DB <sub>7</sub> — DB <sub>0</sub> E <sub>1</sub> 0 0 0 0 1 1 1 * * *                                                                       |         | The interface data length for the upper 2 lines is set to 8 bits. The character format becomes 5 x 7 dotmatrix at 1/16 duty cycle.                           |

| 3   | Function Set  E RS R/W DB <sub>7</sub> — DB <sub>0</sub> E <sub>2</sub> 0 0 0 0 1 1 1 * * *                                                                       |         | The interface data length for the lower 2 lines is set to 8 bits. The character format becomes 5 x 7 dotmatrix at 1/16 duty cycle.                           |

| 4   | E         RS         R/W         DB <sub>7</sub> —         DB <sub>0</sub> E <sub>1</sub> 0         0         0         0         1         1         0           |         | The display for the lower 2 lines and cursor are turned ON, but nothing is displayed.                                                                        |

| 5   | E         RS         R/W         DB <sub>7</sub> —         DB <sub>0</sub> E <sub>2</sub> 0         0         0         0         1         1         0         0 | _       | The display for the upper 2 lines is turned ON and the cursor is turned OFF, but nothing is displayed.                                                       |

| 6   | Entry Mode Set  E RS R/W DB <sub>7</sub> — DB <sub>0</sub> E <sub>1</sub> 0 0 0 0 0 0 1 1 0                                                                       |         | The address is incremented by one and the cursor shifts to the right in a write operation to internal RAM for the upper 2 lines. The display is not shifted. |

| No. | Instruction                                                                                              | Display           | Operation                                                                                                                                                    |

|-----|----------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Entry Mode Set  E R5 R/W DB <sub>7</sub> — DB <sub>0</sub> E <sub>2</sub> 0 0 0 0 0 0 1 1 0              | _                 | The address is incremented by one and the cursor shifts to the right in a write operation to internal RAM for the lower 2 lines. The display is not shifted. |

| 8   | Write to CG RAM or DD RAM  E R5 R/W DB <sub>7</sub> — DB <sub>0</sub> E <sub>1</sub> 1 0 0 1 0 0 1 1 0 0 | L_                | L is written. The AC is incremented by one and the cursor shifts to the right.                                                                               |

| 9   |                                                                                                          |                   |                                                                                                                                                              |

| 10  | Write to CG RAM or DD RAM  E RS R/W DB <sub>7</sub> — DB <sub>0</sub> E <sub>1</sub> 1 0 0 0 1 1 0 1 0 0 | LCD MODULE M4024_ | 4 is written.                                                                                                                                                |

| 11  | DD RAM address set  E RS R/W DB <sub>7</sub> — DB <sub>0</sub> E <sub>1</sub> 0 0 1 1 0 0 0 0 0 0        | LCD MODULE M4024  | The DD RAM address is set so that the cursor appears at digit 1 of line 2.                                                                                   |

| 12  | Write to CG RAM or DD RAM  E RS R/W DB <sub>7</sub> — DB <sub>0</sub> E <sub>1</sub> 1 0 0 0 1 1 0 1 0 0 | LCD MODULE M4024  | 4 is written.                                                                                                                                                |

| No. | Instruction                                                                                                                                                                                        | Display                             | Operation                                                                  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------|

| 13  |                                                                                                                                                                                                    |                                     |                                                                            |

| 14  | Write to CG RAM or DD RAM  E RS R/W DB <sub>7</sub> — DB <sub>0</sub> E <sub>1</sub> 1 0 0 1 0 1 0 0 1 1                                                                                           | LCD MODULE M4024 40DIGITS,4LINES_   | S is written.                                                              |

| 15  | Display ON/OFF Control           E         RS         R/W         DB <sub>7</sub> —         DB <sub>0</sub> E <sub>1</sub> 0         0         0         0         1         1         0         0 | LCD MODULE M4024 40DIGITS,4LINES    | The cursor for the upper 2 lines are turned OFF.                           |

| 16  | DD RAM address set  E RS R/W DB <sub>7</sub> — DB <sub>0</sub> E <sub>2</sub> 0 0 1 0 0 0 0 0 0 0                                                                                                  | LCD MODULE M4024 40DIGITS,4LINES    | The DD RAM address is set so that the cursor appears at digit 1 of line 3. |

| 17  | E         RS         R/W         DB <sub>7</sub> —         DB <sub>0</sub> E <sub>2</sub> 0         0         0         0         1         1         1         0                                  | LCD MODULE M4024 40DIGITS,4LINES    | The cursor is turned ON at digit 1 of line 3.                              |

| 18  | Write to CG RAM or DD RAM  E RS R/W DB <sub>7</sub> — DB <sub>0</sub> E <sub>2</sub> 1 0 0 1 0 0 1 0 0 0                                                                                           | LCD MODULE M4024 40DIGITS,4LINES H_ | H is written.                                                              |

| No. | Instruction                                                                                              | Display                                             | Operation                                                                  |

|-----|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------|

| 19  | Write 10 CG RAM or DD RAM  E RS R/W DB <sub>7</sub> — DB <sub>0</sub> E <sub>2</sub> 1 0 0 1 0 0 1 0 0 1 | LCD MODULE M4024 40DIGITS,4LINES HI_                | I is written.                                                              |

| 20  |                                                                                                          |                                                     |                                                                            |

| 21  | Write to CG RAM or DD RAM  E R5 R/W DB7 — DB0  E2 1 0 0 1 0 1 0 1 0 0                                    | LCD MODULE M4024 40DIGITS,4LINES HIGH CONTRAST_     | T is written.                                                              |

| 22  | DD RAM address set    E   RS   R/W   DB <sub>7</sub> DB <sub>0</sub>                                     | LCD MODULE M4024 40DIGITS,4LINES HIGH CONTRAST      | The DD RAM address is set so that the cursor appears at digit 1 of line 4. |

| 23  | Write to CG RAM or DD RAM  E RS R/W DB <sub>7</sub> — DB <sub>0</sub> E <sub>2</sub> 1 0 0 1 0 1 0 1 1 1 | LCD MODULE M4024 40DIGITS,4LINES HIGH CONTRAST W_   | W is written                                                               |

| 24  | Write to CG RAM or DD RAM  E RS R/W DB <sub>7</sub> — DB <sub>0</sub> E <sub>2</sub> 1 0 0 1 0 0 1 0 0 1 | LCD MODULE M4024 40DIGITS, 4LINES HIGH CONTRAST WI_ | l is written                                                               |

| No. | Instruction                                                                                                                                                                              | Display                                                            | Operation                                     |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------|

| 25  |                                                                                                                                                                                          |                                                                    |                                               |

| 26  | Write to CG RAM or DD RAM  E RS R/W DB <sub>7</sub> — DB <sub>0</sub> E <sub>2</sub> 1 0 0 1 0 0 0 1 0 1                                                                                 | LCD MODULE M4024 40DIGITS,4LINES HIGH CONTRAST WIDE VIEWING ANGLE_ | E is written.                                 |

| 27  | Display ON/OFF Control           E         RS         R/W         DB <sub>7</sub> —         DB <sub>0</sub> E <sub>2</sub> 0         0         0         0         1         1         0 | LCD MODULE M4024 40DIGITS,4LINES HIGH CONTRAST WIDE VIEWING ANGLE  | The cursor is turned OFF.                     |

| 28  | DD RAM address set  E RS R/W DB <sub>7</sub> — DB <sub>0</sub> E <sub>1</sub> 0 0 1 0 0 0 0 0 0 0                                                                                        | LCD MODULE M4024 40DIGITS,4LINES HIGH CONTRAST WIDE VIEWING ANGLE  | The DD RAM address is set at line 1.          |

| 29  | Display ON/OFF Control  E RS R/W DB <sub>7</sub> — DB <sub>0</sub> E <sub>1</sub> 0 0 0 0 0 1 1 1 0                                                                                      | LCD MODULE M4024 40DIGITS,4LINES HIGH CONTRAST WIDE VIEWING ANGLE  | The cursor is turned ON at digit 1 of line 1. |

| 30  |                                                                                                                                                                                          |                                                                    |                                               |

# 2.5.2 Interface data length: Four bits

| No. | Instruction                                                                                                               | Display | Operation                                                                                                                                            |

|-----|---------------------------------------------------------------------------------------------------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Power-on  E RS R/W DB <sub>7</sub> — DB <sub>4</sub>                                                                      |         | The built-in reset circuit initializes the module.                                                                                                   |

| 2   | Function Set  E RS R/W DB <sub>7</sub> — DB <sub>4</sub> E <sub>1</sub> 0 0 0 0 1 0                                       |         | Four-bit operation mode is set for the upper 2 lines. *Eight-bit operation mode is set by initialization, and the instruction is executed only once. |

| 3   | Function Set  E RS R/W DB <sub>7</sub> — DB <sub>4</sub> E <sub>1</sub> 0 0 0 0 1 0  E <sub>1</sub> 0 0 1 * * *           |         | The 4-bit operation mode, 1/16 duty cycle, and 5 x 7 dot-matrix character format are selected. Then 4-bit operation mode starts.                     |

| 4   | Function Set  E RS R/W DB <sub>7</sub> — DB <sub>4</sub> E <sub>2</sub> 0 0 0 0 1 0                                       |         | Four-bit operation mode is set for the lower 2 lines. *Eight-bit operation mode is set by initialization, and the instruction is executed only once. |

| 5   | Function Set  E RS R/W DB <sub>7</sub> — DB <sub>4</sub> E <sub>2</sub> 0 0 0 0 1 0  E <sub>2</sub> 0 0 1 * * *           |         | The 4-bit operation mode, 1/16 duty cycle, and 5 x 7 dot-matrix character format are selected. Then 4-bit operation mode starts.                     |

| 6   | Display ON/OFF Control  E RS R/W DB <sub>7</sub> — DB <sub>4</sub> E <sub>1</sub> 0 0 0 0 0 0  E <sub>1</sub> 0 0 1 1 1 0 |         | The display of the upper 2 lines and cursor are turned ON, but nothing is displayed.                                                                 |

| No. | Instruction                                                                                                                                                                                            | Display          | Operation                                                                                                                                                    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | E         RS         R/W         DB <sub>7</sub> DB <sub>4</sub> E <sub>2</sub> 0         0         0         0         0           E <sub>2</sub> 0         0         1         1         0         0 | _                | The display of the lower 2 lines is turned ON and the cursor is turned OFF, but nothing is displayed.                                                        |

| 8   | Entry Mode Set  E RS R/W DB <sub>7</sub> — DB <sub>4</sub> E <sub>1</sub> 0 0 0 0 0 0  E <sub>1</sub> 0 0 0 1 1 0                                                                                      |                  | The address is incremented by one and the cursor shifts to the right in a write operation to internal RAM for the upper 2 lines. The display is not shifted. |

| 9   | Entry Mode Set  E RS R/W DB <sub>7</sub> — DB <sub>4</sub> E <sub>2</sub> 0 0 0 0 0 0  E <sub>2</sub> 0 0 0 1 1 0                                                                                      | _                | The address is incremented by one and the cursor shifts to the right in a write operation to internal RAM for the lower 2 lines. The display is not shifted. |

| 10  | Write to CG RAM or DD RAM  E RS R/W DB <sub>7</sub> — DB <sub>4</sub> E <sub>1</sub> 1 0 0 1 0 0  E <sub>1</sub> 1 0 1 1 0 0                                                                           | L                | L is written. The AC is incremented by one and the cursor shifts to the right.                                                                               |

| 11  |                                                                                                                                                                                                        |                  |                                                                                                                                                              |

| 12  | E         RS         R/W         DB <sub>7</sub> DB <sub>4</sub> E <sub>2</sub> 0         0         0         0         0           E <sub>2</sub> 0         0         1         1         1         0 | LCM 40X4 SEIKO I | The display of the lower 2 lines and cursor are turned ON, but nothing is displayed                                                                          |

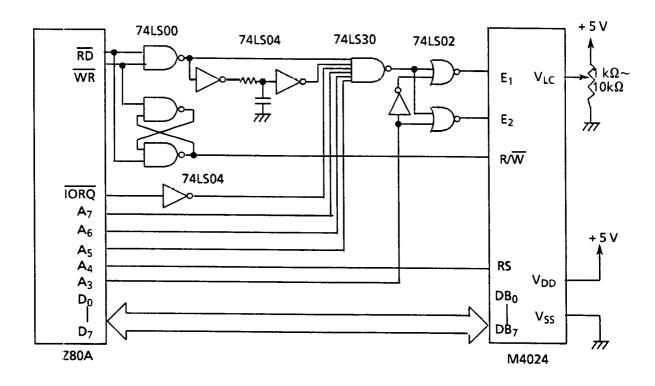

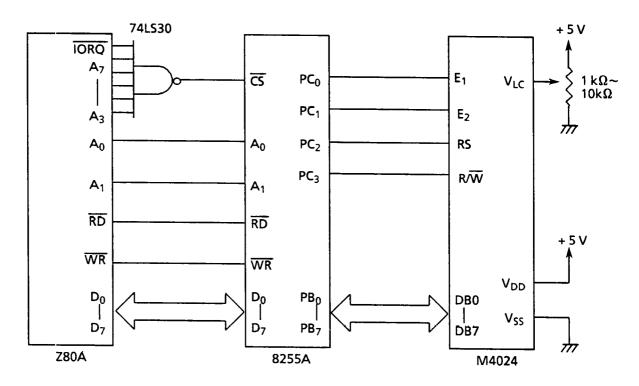

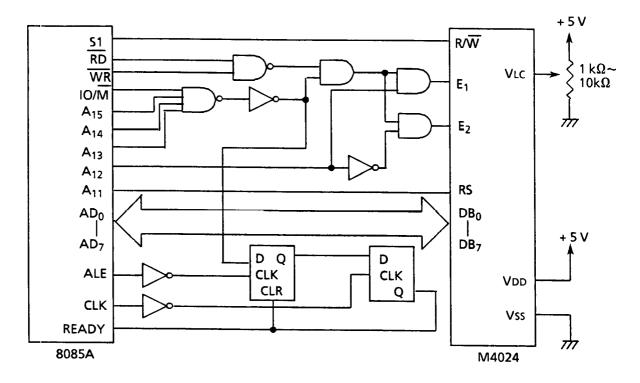

# 2.6 MPU Connection Diagrams

# 2.6.1 Z80A

## 2.6.2 Z80A and 8255A

# 2.6.3 8085A

## 2.6.4 6809

#### 3. NOTES

#### Safety

• If the LCD panel breaks, be careful not to get the liquid crystal in your mouth. If the liquid crystal touches your skin or clothes, wash it off immediately using soap and plenty of water.

#### Handling

- · Avoid static electricity as this can damage the CMOS LSI.

- · The LCD panel is plate glass; do not hit or crush it.

- · Do not remove the panel or frame from the module.

- · The polarizer of the display is very fragile; handle it very carefully.

#### Mounting and esign

- · Mount the module by using the specified mounting part and holes.

- · Connect a 10-µF capacitor between the power supply terminals to eliminate noise.

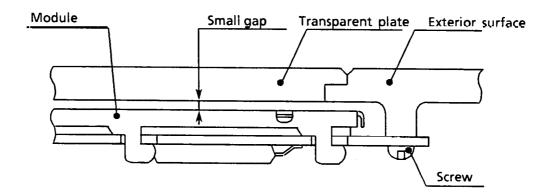

- To protect the module from external pressure, place a transparent plates (e.g. acrylic or glass), leaving a small gap, over the display surface, frame, and polarizer.

#### ☆Example

- Design the system so that no input signal is given unless the power-supply voltage is applied.

- · Keep the module dry. Avoid condensation, otherwise the transparent electrodes may break.

## Storage

- Store the module in a dark place where the temperature is  $25^{\circ}\text{C}$   $\pm 10^{\circ}\text{C}$  and the humidity below 65% RH.

- · Do not store the module near organic solvents or corrosive gases.

- · Do not crush, shake, or jolt the module (including accessories).

#### Cleaning

- · Do not wipe the polarizer with a dry cloth, as it may scratch the surface.

- · Wipe the module gently with a soft cloth soaked with a petroleum benzine.

- Do not use ketonic solvents (ketone and acetone) or aromatic solvents (toluene and xylene), as they may damage the polarizing plate.